关注 ▲射频工程师的日常▲ ,一起学习

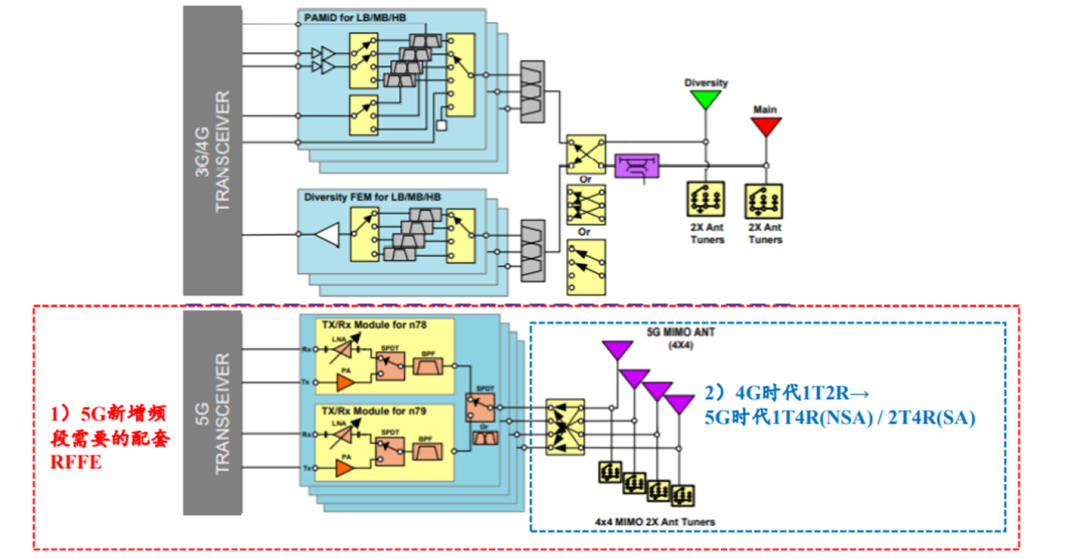

目前主流的4G 射频前端架构,多采用 TRX(接收通路+发射通路)+DRX(分集接收)实现 1T2R 模式,且TRX 和 DRX通路都由集成模块实现。简单说就是按照频率高低,将各频段集成入6~8个模组中,即GSM/LB/MB/HB

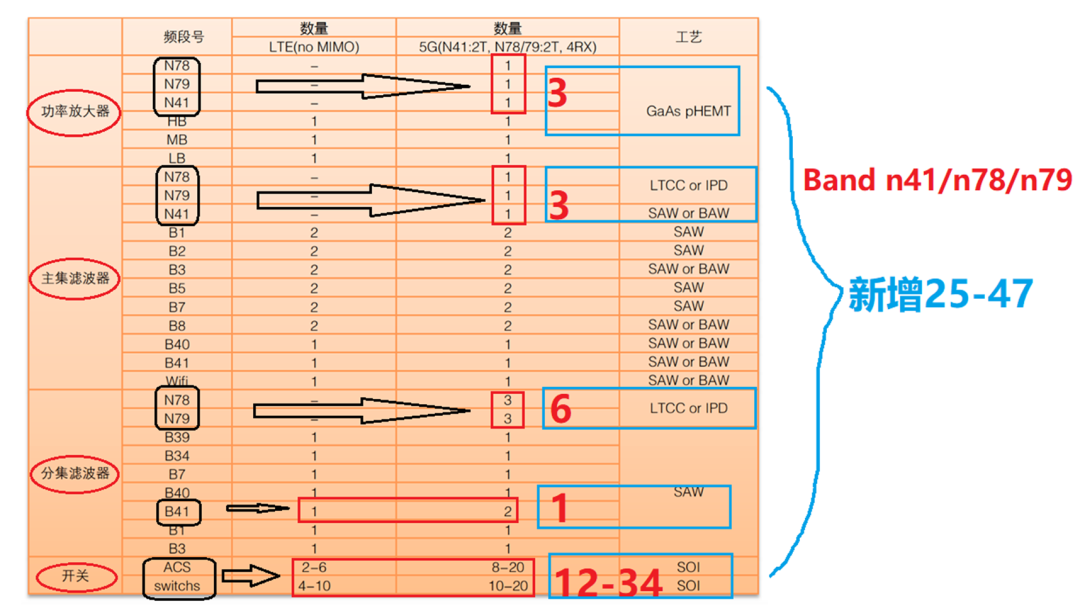

PAMID 模组和 GSM/LB/MB/HB Diversity FEM 模组。而5G需要增加射频前端器件与之配套,至少需要新增n78/n79两个频段对应的通路,在 NSA 标准下是1T4R,在 SA 标准下是2T4R。

5G引入了4*4

MIMO、SRS和EN-DC等功能,要求射频前端的接收端必须具备单频段四路接收的能力,相较于4G使用的两路接收方案,价格提升了229%。

以国内5G手机为例,高端机型普遍采用221方案,即2路N41、2路N78和1路N79主集芯片,接收端相应需要额外的2路N41、2路N78和3路N79分集芯片;中低端机型发射端普遍采用211方案,即2路N41、1路N78和1路N79主集芯片,则接收端需要额外的2路N41、3路N78和3路N79分集芯片。主集芯片大多采用PAMid方案,供应商为国外的高通、Qorvo、Sky;分集芯片是国内厂商最大的机会,国内的卓胜微、唯捷创芯、昂瑞微有望进入国内Tier1

OEM供应商名单。基带芯片的硬件架构采用MCU+DSP+ASIC的形式。硬件是基带芯片的躯体,决定了基带性能的下限。

MCU主要用于运行基带协议栈代码,目前主流的基带MCU多采用ARM内核,主要是Cortex A系列和Cortex R系列。另外,为了降低基带芯片功耗,还会额外采用一颗Cortex

M作为基带芯片在飞行模式、待机等低功耗场景下的MCU;

DSP是基带芯片的核心硬件,用来实现无线通信物理层(L1)核心算法。主要功能有编解码、FFT/iFFT、CRC校验等,DSP决定了基带芯片数据吞吐能力。DSP有自行研发和IP授权两种,高通、MTK、海思采用自研方案,其他厂商采用Ceva公司的IP授权;

ASIC包括基带芯片内部调试接口,外围接口等附属功能的实现,这类芯片复杂度较低,一般采用IP授权的方式。

基带芯片软件主要有实时操作系统(RTOS)、驱动程序(Drivers)和协议栈(Protocol

Stack),协议栈是基带软件的核心。软件是基带芯片的灵魂,决定了芯片的性能上限。

文章评论