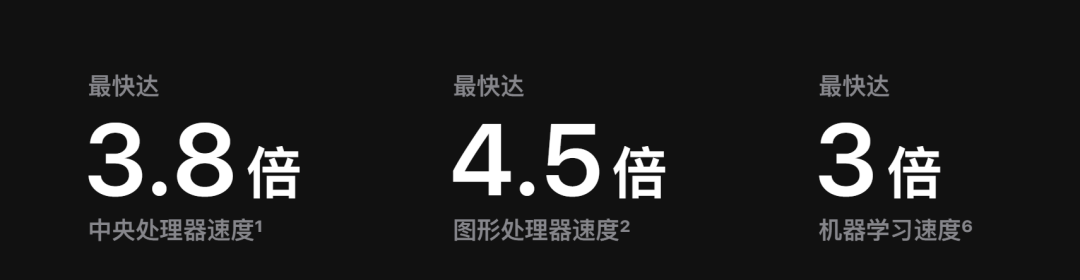

今年,苹果把两片 M1 Max 粘在一块,做成了秒天秒地的 M1 Ultra。

粘在一起后,在核心的工艺没变的情况下,性能大幅提升了!

之前谈芯片工艺制程的时候,很多机友会问,当芯片工艺到 1nm 之后,性能要怎么提升?

之前谈芯片工艺制程的时候,很多机友会问,当芯片工艺到 1nm 之后,性能要怎么提升?

呐,现在还没到 1nm,不就可以在工艺不变的情况下提升性能了吗!

这一回,好像又是苹果忽然之间找到了一条能让性能提升的分岔路。

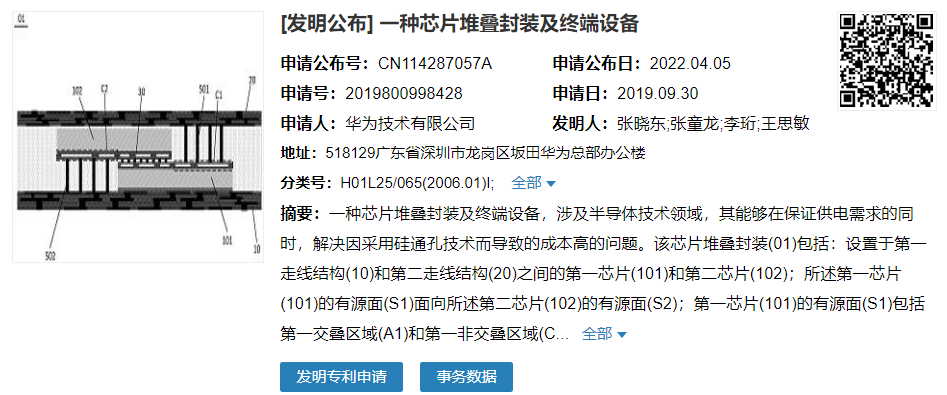

而最近,华为也公开了“粘芯片”的专利。

好像苹果的入场,让大家一下子盯准了这个方案。

又一次引领行业。

但是啊,事实并不全是酱紫的。

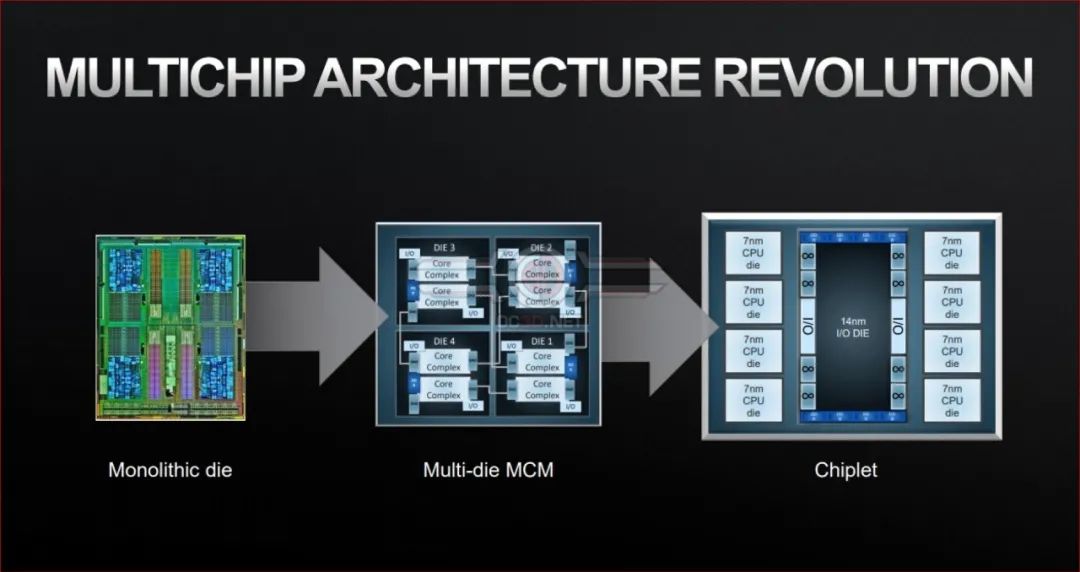

苹果用的这个粘芯片的技术,属于 chiplet,也叫小芯片技术。

一开始,大家有这种想法的时候,差不多算是先把芯片做成模块化。

一开始,大家有这种想法的时候,差不多算是先把芯片做成模块化。

把处理单元、存储、I/O 芯片拆分开来,然后通过先进的封装技术把这些小芯片 3D 封装叠成一块芯片。

这三块的分别组合,形成了厂商们自己的方案。

划重点 —— 两个关键,拆成小芯片以及先进的封装技术。

这技术目前来看至少有三好处。

一是可以做超多核心,性能当然也会比单一芯片强,这个 M1 Ultra 不用多说了吧。

二是有些方案比直接装两块芯片进去面积要小。

三是利用好了成本反而会降低。

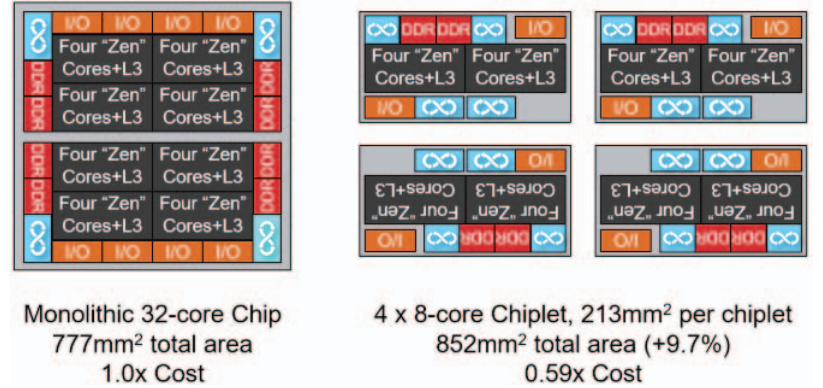

之前 AMD 团队给过一个案例,在 14nm 的情况下,以小芯片技术分别生产的成本,相较于单芯片直接集成生产,可以降低超过 40%。

这种小芯片技术还被部分厂商认为,是解决摩尔定律失效的方案。

这种小芯片技术还被部分厂商认为,是解决摩尔定律失效的方案。

摩尔定律:集成电路上可容纳的晶体管数目,约每隔两年便会增加一倍

往后还延伸到芯片成本,每隔一年半成本可降低五成,平均每年成本可降低三成多

简单地说,它能够在工艺即将到顶的时候,在一定程度上,满足晶体管数量增加一倍,性能进一步提升的这个需求。

这种用好了既能省钱,又能提升性能的技术,根本不用等苹果,大家伙老早就开始搞了。

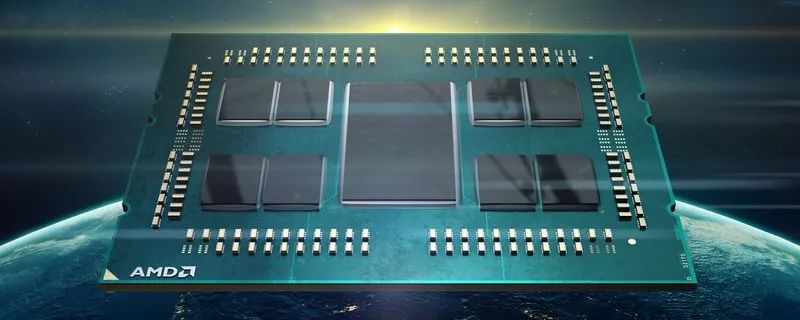

早在 M1 Ultra 之前,AMD、英特尔、华为、亚马逊,都有小芯片技术的相关技术研究以及量产芯片。

比如 AMD 的 ZEN/Ryzen、英特尔的 sapphire、亚马逊 graviton。

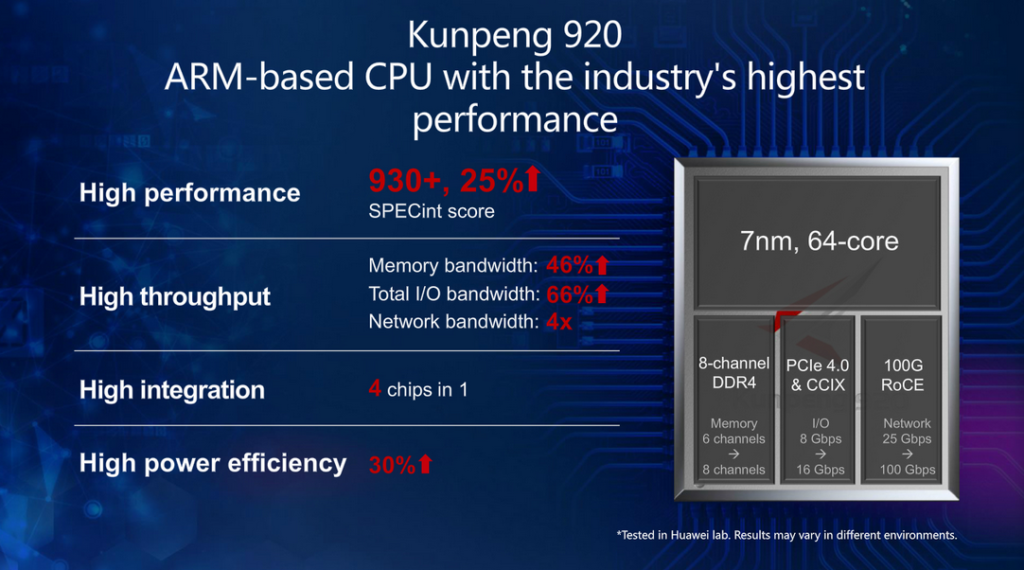

除此之外,业界性能最强的华为鲲鹏 920,也是用这个技术做的。

聊到华为,大家就不困了吧。

华为

和目前其它几家钻研小芯片技术的厂商不同,华为在芯片上是受到限制的。

其他几家可能考虑更多的是通过各种办法,解决先进制程价格贵、解决摩尔定律失效这两个问题。

但对于华为而言,除了鲲鹏 920 这种服务器芯片外,还要考虑能不能顺手缓解一下,手机没自家芯片用的问题。

之前,华为让中芯国际以 14nm 工艺做过一颗芯片 —— 麒麟 710A。

它的架构和麒麟 970 差不多,都是 4×A73+4×A53,大核主频低了 0.4GHz。

它的架构和麒麟 970 差不多,都是 4×A73+4×A53,大核主频低了 0.4GHz。

主要劣势还是 GPU,只有四核的 Mali-G51。

由于各种问题,这颗芯片最后的安兔兔跑分只有 14 万分左右。

现在,中芯国际升级到了 FinFET N+1 工艺,能够实现接近 10nm 的效果。

更有 N+2 工艺,有希望实现接近 7nm 的性能。

不过,中芯 2021 财报中,却没有了 N+2 工艺研发的部分。

所以它最顶级的工艺,就只能做到接近 10nm 的性能。

华为:不够用啊朋友。

回顾一下,小芯片技术的特性是什么?

是在工艺不提升的情况下,通过多芯片堆叠,提升晶体管数量,增强性能。

那华为是不是可以通过芯片堆叠这个技术,让 14nm 甚至接近 10nm 的芯片堆叠起来,实现更强的性能。

14nm+14nm=7nm 是虚的,那 ≈7nm 或者 >10nm 呢?

14nm+14nm=7nm 是虚的,那 ≈7nm 或者 >10nm 呢?

以机哥目前检索到的资料来说,应该可以。

但,问题不小。

小芯片技术的关键 —— 先进封装,其最顶级的方案,还是在台积电手里。

以苹果的 M1 Ultra 来说,它最牛逼的,不是把两块芯片叠在一起。

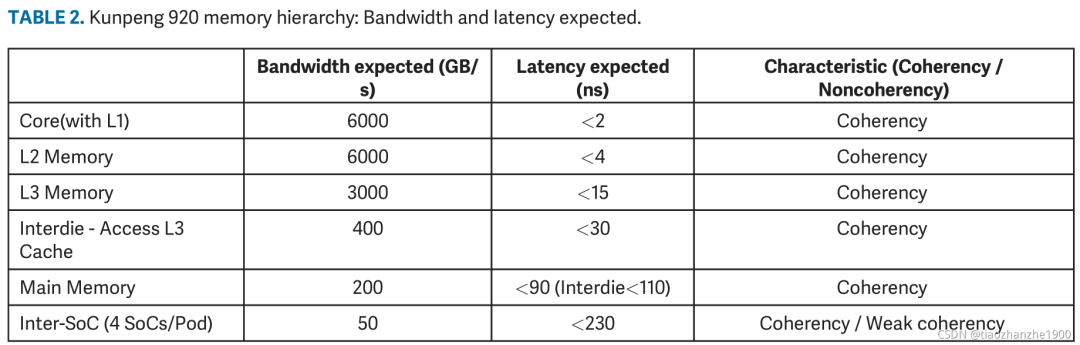

而是 —— 实现了芯片之间,高达 2.5TB/s 的互联带宽。

这是目前业界做小芯片技术里面最快的了。

华为鲲鹏是 400GB/s,AMD ZEN3 是 140GB/s。

以这个超高的互联带宽,作为两颗芯片性能叠加的基础,是技术的关键之一。

以这个超高的互联带宽,作为两颗芯片性能叠加的基础,是技术的关键之一。

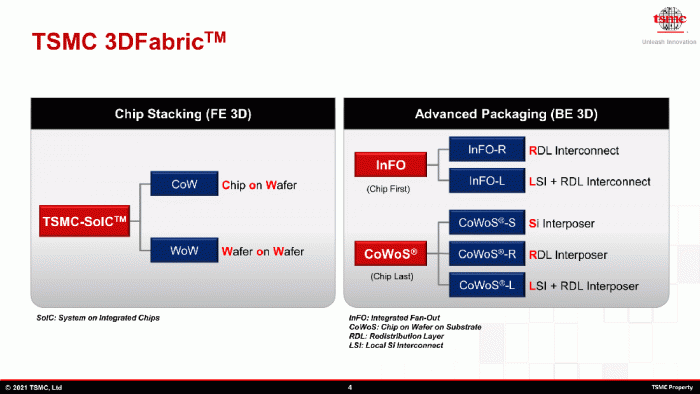

M1 Ultra 使用的封装技术,可能是这两个里的一个:CoWoS-L 和 InFO-L。

这两种,都是台积电的 3D 封装技术。

除了苹果,AMD 用的也是台积电方案。

早在 2015 年就用 HBM 技术发布了 Fury X 显卡,几乎称得上是最早开始搞小芯片技术的 AMD。

目前绝大部分的 3D 封装技术,也来自台积电。

包括去年发布的 3D V-Cache 技术,也是基于台积电的先进封装做的。

包括去年发布的 3D V-Cache 技术,也是基于台积电的先进封装做的。

和掌握 7nm、5nm、3nm 等先进制程一样,顶级的先进封装技术也掌握在台积电的手里。

甚至说,未来很长一段时间也会是台积电的特长。

目前,喊得上名字的顶级大厂里,只有英特尔和三星有在先进封装上有所布局。

英特尔 2021 投入巨大。

不过,不少人预测英特尔在未来很有可能也会转回像 AMD 一样只做芯片设计而不生产芯片的 Fabless(无厂半导体)型厂商。

至于三星咧?

就给大家看两个报道的节选:

就给大家看两个报道的节选:

-

2021 年三星决定布局先进封装,为的是和台积电竞争。

-

2022 年,三星又重新考虑先进封装是否需要产线了,因为高通和三星自己目前都不感兴趣。

其它的封装厂也有方案,但未来短时间内,先进封装大概还会是台积电、英特尔主导。

做小芯片技术的关键是什么?是核心单元的拆分和设计,以及先进封装技术。

这些封装技术都在英特尔和台积电手里…那华为面对的还是现在的困境。

可以自己做芯片的设计,也能自己做芯片堆叠的设计。

但老问题依然在,谁来生产?

但老问题依然在,谁来生产?

有些机友可能会问,中芯呢?

中芯国际确实可以生产 14nm 的芯片,但他可能没法处理先进封装。

这是生产上的问题。

还有小芯片技术本身的问题。

它是个更适合给大芯片做的技术,无论是成本考虑还是技术本身考虑,看起来都更适合大芯片。

两颗芯片的内核解构一下,堆叠封装在一个芯片里头,先不说性能是不是 ×2,功耗和发热首先得是 ×2 的。

做电脑、服务器的处理器倒还好,毕竟可以加装主动散热,电源也可以几百瓦往上冲。

做电脑、服务器的处理器倒还好,毕竟可以加装主动散热,电源也可以几百瓦往上冲。

你试想一下把两颗骁龙 888 拆开像 M1 Ultra 那样封起来,封装成这样的芯片,再塞进手机里头…

且不讨论体积了,这功耗、这发热,不得上个水冷?

接着是成本,目前手机 CPU 可能根本扛不住先进封装+双芯片堆叠的成本。

大家要搞明白,相比起普通封装,先进封装本身是更贵的。

业内人士计算过,小芯片技术在两种情况下才会获得收益,一个是做大芯片,一个是做最领先的先进工艺。

大芯片有一部分原因是芯片本身很贵,如果做成一片式生产,其中一个元器件出问题导致整个芯片都废掉的成本,比先进封装带来的成本要高。

大芯片有一部分原因是芯片本身很贵,如果做成一片式生产,其中一个元器件出问题导致整个芯片都废掉的成本,比先进封装带来的成本要高。

先进工艺机哥理解大概就是造不出更好,或者用下一级工艺来造出更好的芯片时,价格更贵了。

这时候可以用先进封装来获得更强的性能。

可是华为能用的只有中芯国际的 14nm 以及接近 10nm 的 N+1 方案。

这样在堆叠一下,或许会变成用 5nm 芯片的价格,做出来接近 7nm 芯片的性能…

这样面对 5nm 的竞品时,既没有性能优势,也没有价格优势。

这两个理由也解释了为什么现在三星电子和骁龙都看不上先进封装。

chiplet 和先进封装是好东西,它也是未来的趋势,所以华为也在搞。

但是华为目前的方向还是做服务器的芯片,而不是做手机的芯片。

感兴趣的可以去研究研究鲲鹏 920,性能很顶。

至于 chiplet 做手机芯片,能不能帮到华为手机,还是再等等看。

图片来自网络

封杀这事儿真的太狗了

↘↘↘

文章评论